|

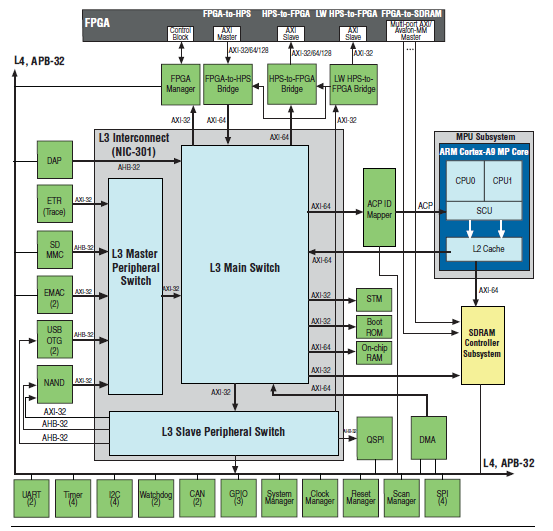

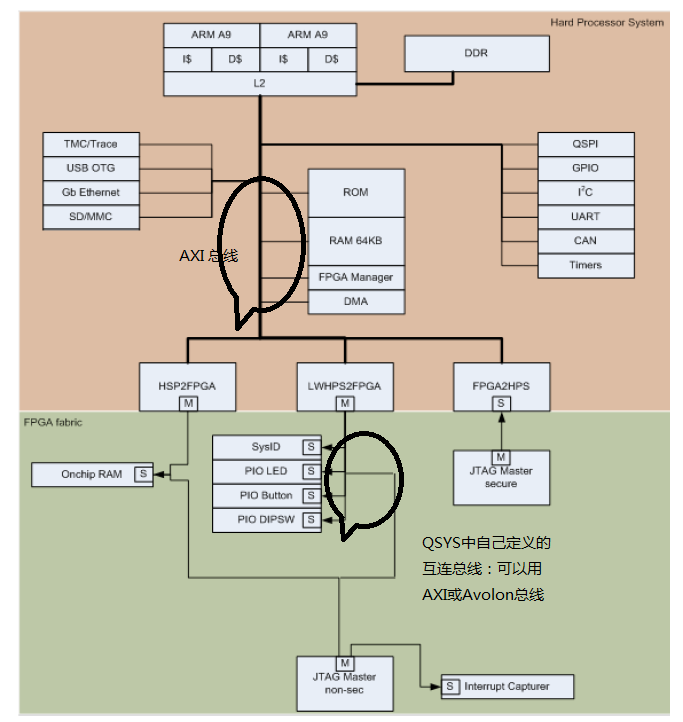

在Altera SoC FPGA系统中,有两种不同的外设连接方式,一种是ARM 通过AXI总线连接的外设,(可以成为硬外设),另外有一种是通过FPGA连接的外设,

在SoC FPGA中,通过FPGA连接的外设是通过LW HPS to FPGA Bridge连接的,整个系统如下图所示:

如果要通过ARM驱动与FPGA相连的外设,需要经过以下几个步骤:

1、初始化LW HPS to FPGA Bridge,目前Altera开发包提供了alt_bridge_init()函数,在函数中主要通过

以下几个步骤进行初始化:

A)通过复位管理器RSTManager,对总线桥进行复位操作;

B)通过时钟管理器进行使能桥的时钟配置;

2、对相应的周边设备地址进行复制,驱动相关外设,目前Altera开发包提供了相应的alt_write_word()函数,

其中需要注意的是在QSYS中,与FPGA互连的外设地址是一个偏移地址,其基地址为LW HPS to FPGA Bridge的地址,

|